探究CPCI總線的PMC載板設計

2021-07-01 10:02:21

admin

摘 要:設計了一種基于CPCI總線標準的PMC接口載板。載板以FPGA為核心,集成了CPCI接口模塊和DPRAM(雙口RAM)模塊,CPCI接口模塊采用FPGA+PCI IP核(軟核)解決了系統(tǒng)集成的問題,DPRAM模塊為系統(tǒng)提供了數(shù)據(jù)緩存功能。環(huán)回測試和中斷測試解決了在沒有子卡PMC模塊的情況下,讀寫、驗證DPRAM空間數(shù)據(jù)和測試中斷響應的問題。此外,還支持子卡PMC模塊后出線到CPCI總線。調(diào)試結(jié)果表明,該載板在嵌入式實時操作系統(tǒng)VxWorks下可以穩(wěn)定運行,正確地讀寫DPRAM空間的數(shù)據(jù),及時地響應中斷,滿足了對載板的性能需求。

Compact PCI(Compact Peripheral Component Interconnect)簡稱CPCI,中文又稱緊湊型PCI,是國際工業(yè)計算機制造者聯(lián)合會PICMG(PCI Industrial Computer Manufacturer′s Group)于1994提出來的一種總線接口標準,是以PCI電氣規(guī)范為標準的高性能工業(yè)用總線[1]。CPCI規(guī)范改進自PCI電氣規(guī)范2.1,應用于工業(yè)和嵌入式領域。當前最新的CPCI規(guī)范是PICMG 3.0。PICMG 3.0主要將應用在高帶寬電信傳輸上,以適應未來電信的發(fā)展,PICMG 2.x則仍是目前CPCI的主流,并將在很長時間內(nèi)主宰CPCI的應用。

PCI夾層卡PMC(PCI Mezzanine Cards)是IEEE P1386.1的標準,作為一個IEEE標準,PMC確保了任何符合該標準的主板或者模塊能夠與其他按照該標準設計的主板或者模塊兼容[2]。這樣就為用戶提供了很大的柔性,用戶可以任意組合和搭配不同的主卡和模塊。PMC是個開放標準,它為Multibus II、VME和Compact PCI帶來了前所未有的大量I/O產(chǎn)品和高性能。

本文結(jié)合實際的工程項目,設計實現(xiàn)一個基于CPCI總線并符合PICMG 2.0規(guī)范的6U(233.35 mm×160 mm)通用型PMC載板FTC-C920并開發(fā)其在VxWorks 5.5下的驅(qū)動軟件。

1 載板總體結(jié)構(gòu)設計

本著簡潔和通用的前提,此載板主要由電源模塊(Power)、PMC接口模塊(J11~J14)、CPCI總線接口模塊(J1、J4、J5)和FPGA組成,總體結(jié)構(gòu)如圖1所示。

2 PMC接口和CPCI總線接口模塊設計

PMC接口的特性為:前兩個(“P11”和“P12”)用于32位PCI信號,第3個(“P13”)是64位PCI信號需要。一個額外的總線連接器(“P14”),可用于非指定的I/O信號[2]。本設計中,PMC接口模塊采用4個(J11~J14)PMC(PCI Mezzanine Cards)8 mm高標準連接器,支持用戶子卡PMC后出線到CPCI總線接口J4和J5。圖1給出了板卡的CPCI連接器情況,J1用作32位PCI,J4和J5用作后面板I/O,可自定義[1]。

3 FPGA設計

從圖2中可以清楚地看到,F(xiàn)PGA主要被設計集成了PCI接口模塊(PCI Slave IP CORE)和DPRAM模塊。

3.1 PCI接口模塊設計

3.1.1 幾種PCI接口設計方案及選擇

常見的設計方案有:(1)專用的PCI接口芯片+CPLD;(2)ASIC+CORE;(3)專用的FPGA+PCI IP CORE(硬核);(4)專用的FPGA+PCI IP CORE(軟核);(5)帶PCI接口的DSP[3]。

幾種方案各有利弊,本文結(jié)合項目的實際應用需求選擇了第4種方案,這個方案滿足了系統(tǒng)集成的需求,并可自由添加接口邏輯,降低了成本,減小了設計風險。

3.1.2 具體設計

此模塊主要實現(xiàn)33 MHz工作時鐘、32 bit總線寬度的PCI接口功能,支持內(nèi)存空間及配置空間的讀寫和PCI中斷功能。

PCI配置空間分配[4]:Vendor ID(廠商號)1206,Device ID(設備號)0920,BAR0(基地址)映射為1 MB內(nèi)存空間,其中0x0000~0x3FFF為DPRAM空間,0x4000~0x7FFF為DPRAM環(huán)回測試空間,0x8000以后為控制寄存器。

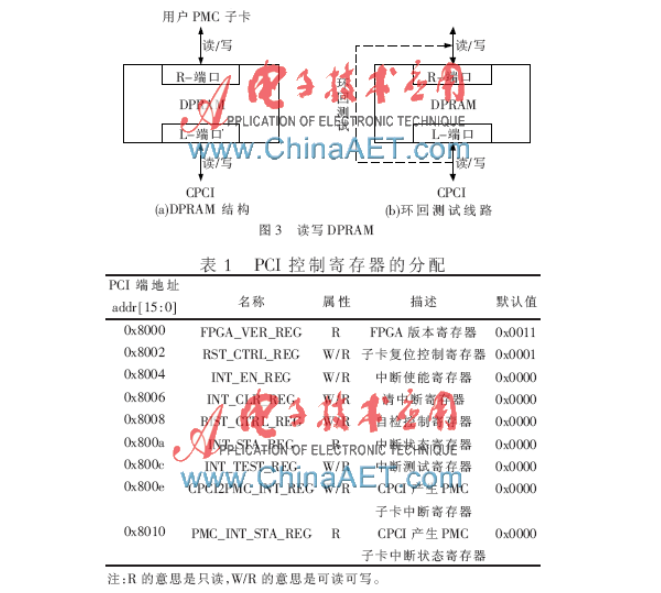

正常情況下(配合用戶PMC子卡使用時),CPCI通過DPRAM左(L)端口對DPRAM空間進行讀寫,用戶子卡則通過DPRAM右(R)端口對DPRAM空間進行讀寫;環(huán)回測試情況下(即沒有用戶PMC子卡的情況下),CPCI可以通過環(huán)回測試空間對DPRAM進行讀寫,即模擬用戶子卡對DPRAM空間進行讀寫。

需要注意的是,0x0000~0x3FFF為DPRAM 16 KB空間,對應DPRAM空間大小為8K×16 bit,而0x4000~0x7FFF為DPRAM環(huán)回測試空間,不是FPGA另外開辟的RAM空間,只是軟件通過這個空間地址在環(huán)回測試下讀寫DPRAM空間(8K×16 bit)。示意圖如圖3所示。

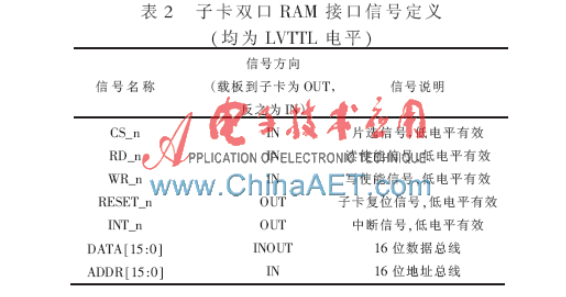

PCI控制寄存器的分配如表1所示。

3.2 DPRAM模塊設計

雙口RAM模塊是FPGA調(diào)用內(nèi)部的IP核實現(xiàn)的,其為數(shù)據(jù)處理提供緩存功能,總線寬度為16 bit,容量為8 K×16 bit。在沒有用戶PMC子卡的情況下,為了驗證對數(shù)據(jù)處理的可用性及準確性,通過FPGA邏輯設計支持雙口RAM R端口環(huán)回自檢,如圖3(b)中虛線所示,即模擬用戶子卡對雙口RAM進行讀寫數(shù)據(jù)的操作。

CPCI和用戶PMC子卡通信采用雙口RAM方式,雙口RAM用戶PMC子卡側(cè)總線定義如表2所示。

4 VxWorks下設備驅(qū)動程序設計

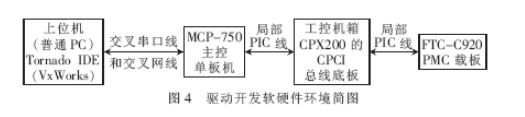

開發(fā)此PMC載板Vxworks 5.5下的驅(qū)動,硬件選用了Motorola公司的實時主控單板機MCP-750、工控機箱CPX2000 series和此PMC載板FTC-C920,操作系統(tǒng)則選擇了美國風河公司的VxWorks嵌入式實時操作系統(tǒng),使用普通的PC,在Tornado IDE(集成開發(fā)環(huán)境)下進行驅(qū)動的開發(fā)。以良好的可靠性和卓越的實時性著稱的VxWorks可以滿足系統(tǒng)對于高實時性和高可靠性的要求[5]。驅(qū)動開發(fā)軟硬件環(huán)境簡圖如圖4所示。

對驅(qū)動程序的設計主要有3個部分:載板自檢測試模塊、FTC-C920和系統(tǒng)控制器互通測試模塊以及CPCI中斷測試模塊。

4.1 載板自檢測試模塊

載板自檢測試主要是載板檢測自身器件是否正常工作,功能是否可以實現(xiàn)。

4.1.1 查找C920載板

對于Vxworks下PCI設備調(diào)試來說,其有專門的函數(shù)可供調(diào)用,查找FTC-C920載板可以通過調(diào)用函數(shù)pciFindDevice()來實現(xiàn),它包含在pciConfigShow庫函數(shù)中,此庫函數(shù)專門用來幫助顯示一些PCI設備的信息。此函數(shù)可以根據(jù)PCI設備給定的供應商標識(VENDOR ID)和設備標識(DEVICE ID)找到相應的設備,并以此返回設備的總線號(busNO)、設備號(deviceNO)和功能號(funcNO)。

4.1.2 讀取FTC-C920上的配置資源信息

根據(jù)獲得的設備的總線號(busNO)、設備號(deviceNO)和功能號(funcNO),通過調(diào)用操作系統(tǒng)庫函數(shù)pciConfigLib中的函數(shù)pciConfigInLong和pciConfigInByte訪問C920的配置空間,獲得設備映射的內(nèi)存基地址(memBase)和I/O基地址(ioBase)以及中斷號irq,分辨對基地址空間是I/O操作還是內(nèi)存操作,獲得的基地址要分別與存儲器屏蔽位PCI_MEMBASE_MASK和I/O屏蔽位PCI_IOBASE_MASK相“與”,才能得到真正板卡的內(nèi)存基地址和I/O基地址。

4.2 FTC-C920和系統(tǒng)控制器互通測試模塊

互通測試主要是:

(1)系統(tǒng)控制器(MCP-750)讀取用戶PMC子卡數(shù)據(jù):用戶PMC子卡向雙口RAM中寫入數(shù)據(jù),系統(tǒng)控制器(MCP0750)從雙口RAM中讀取數(shù)據(jù),并驗證數(shù)據(jù)是否正確。

(2)用戶PMC子卡讀取系統(tǒng)控制器(MCP-750)數(shù)據(jù):系統(tǒng)控制器(MCP-750)向雙口RAM中寫入數(shù)據(jù);用戶PMC子卡從雙口RAM中讀取數(shù)據(jù),并驗證數(shù)據(jù)是否正確。

由于FTC-C920是通用型PMC載板,為了在沒有用戶PMC子卡的情況下驗證互通測試,在FPGA的設計上進行了支持DPRAM R端口環(huán)回自檢的設計,如圖2中虛線所示。

正常情況下(配合用戶PMC子卡使用時),環(huán)回測試空間不可使用,此時FPGA內(nèi)部環(huán)回自檢控制寄存器的相應位為默認值0。如進行環(huán)回自檢(沒有用戶PMC子卡時),需往環(huán)回自檢控制寄存器的相應位寫1,此時,系統(tǒng)控制器可對環(huán)回測試空間進行讀寫。

4.3 CPCI中斷測試模塊

CPCI中斷測試主要是用戶PMC子卡通過寫寄存器的方式產(chǎn)生CPCI中斷;系統(tǒng)控制器響應中斷,讀取數(shù)據(jù)并驗證數(shù)據(jù)是否正確。

在沒有用戶PMC子卡的情況下,可以通過產(chǎn)生內(nèi)部中斷的方式進行測試,具體的方法是在FPGA中設置中斷使能寄存器,中斷測試寄存器,中斷狀態(tài)寄存器和清中斷寄存器。程序流程圖如圖5所示。

本文詳細描述了某項目中PMC載板FTC-C920的設計方法及其在VxWorks操作系統(tǒng)下驅(qū)動程序的開發(fā)流程。在沒有用戶PMC子卡的情況下,通過環(huán)回測試空間的設計,解決了互通測試的要求,通過中斷測試寄存器的設計,解決了中斷測試的要求。調(diào)試結(jié)果表明,此PMC載板在VxWorks 5.5下可以穩(wěn)定地運行。本文的設計方法具有一定的通用性,可為相關工程技術(shù)人員提供可以參考的設計經(jīng)驗。